Out-of-Order RISC-V Processor (SystemVerilog)

EECS 470: Computer Architecture Senior Design | Fall 2025

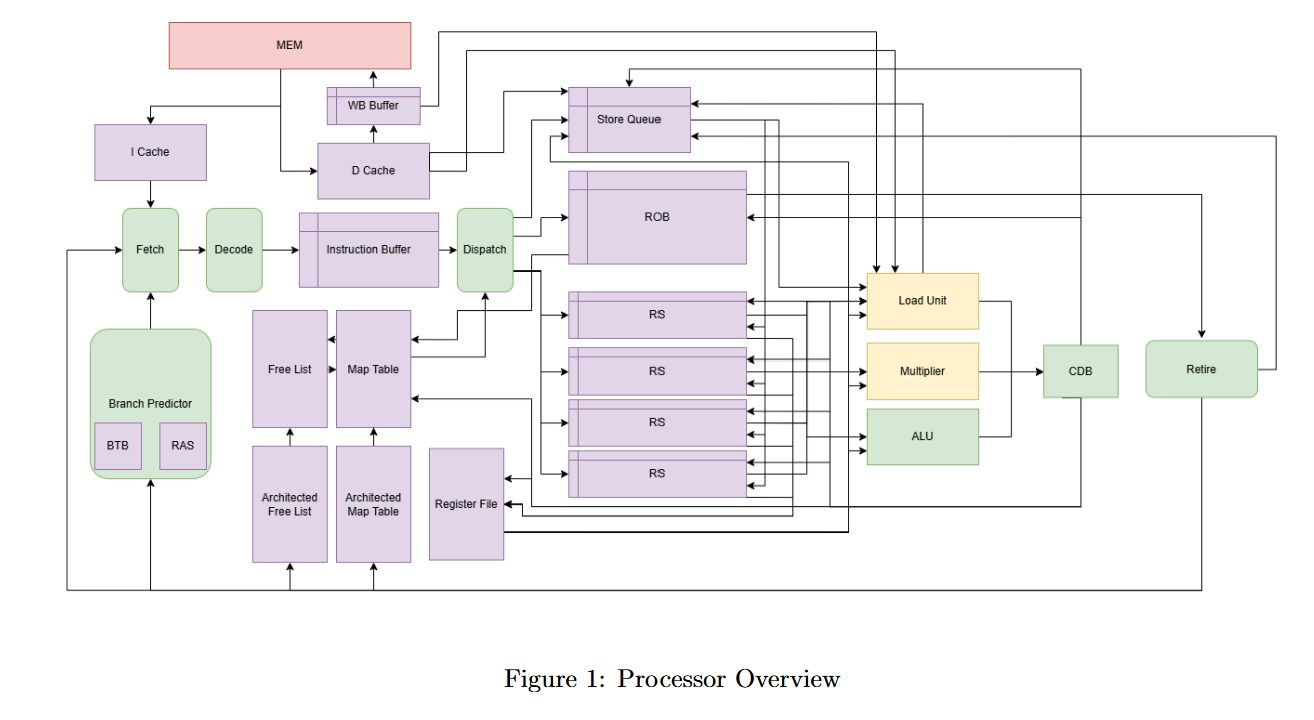

Collaborated on a 5-person team to design and implement a fully synthesizable, N-way superscalar R10K-style out-of-order processor for the RISC-V ISA. My primary contributions included the development and optimization of the Branch Predictor, Free List, Return Address Stack (RAS), as well as testbenching and debugging.

Key Architectural Features:

- N-way Superscalar Execution: Parameterized design allowing multiple instructions to be fetched, issued, and retired per cycle (configured to N=3 for optimal CPI).

- Palacharla Reservation Station: Implemented dependency-based FIFO queues to improve issue logic speed and scalability.

- Advanced Branch Prediction: Integrated a Tournament Predictor (dynamically selecting between PAg and GShare) alongside a 64-entry BTB and a 16-entry Return Address Stack (RAS).

- Early Tag Broadcast: Reduced the wakeup critical path by broadcasting destination tags one cycle before value generation, allowing overlapped wakeup and execution.

- Memory Hierarchy: Developed non-blocking, multi-banked instruction and data caches with a writeback buffer, supporting out-of-order load issues and byte-level store-to-load forwarding.

High-level overview of the processor data flow.